# TMC7300 Datasheet

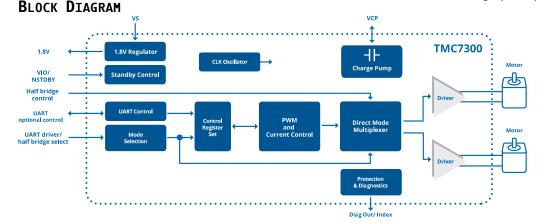

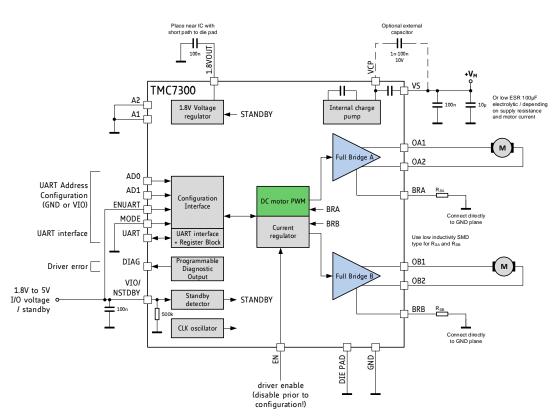

Low Voltage Driver for One or Two DC Motors up to 2A (2.4A) peak - UART based Control for Torque and Velocity. 4 Half Bridge Peripheral Driver Option.

+

#### **FEATURES AND BENEFITS**

Voltage Range 2V (1.8V) ... 11V DC

Battery Operation min. 2 AA / NiMh cells, or 1-2 Li-Ion cells 1 / 2 DC motors up to 2A / 2.4A with velocity & torque control Direct Bridge control for solenoids, relays, lamps, motors... Single Wire UART for two-motor torque and velocity control Standby <50nA typ. current draw Low RDSon LS  $170m\Omega$  & HS  $170m\Omega$  (typ.) Parallel Option for single DC motor Motor Load Feedback available **Full Protection & Diagnostics** Tiny of QFN 3\*3 with 20 pins

| <b>A</b> PPLICATIONS             |

|----------------------------------|

| IOT & Handheld devices           |

| Battery operated motors          |

| 4-Channel Relay- and LED driving |

| Printers, POS                    |

| Toys                             |

| Office and home automation       |

| CCTV, Security                   |

| HVAC                             |

| Mobile medical devices           |

#### DESCRIPTION

Working from a single or dual Li-Ion cell or dual or more AA batteries the TMC7300 is optimally suited for battery operated equipment. Its two full-bridges allow either control of two DC motors, PWM-control of LEDs, or protected standalone peripheral driving, using a polarity signal per halfbridge. Operate up to two DC motors via simple UART control for direction, velocity and torque. Integrated power-MOSFETs with internal charge-pump for best-in-class RDSon even at low supply voltage, handle motor current up to 1.2A per motor continuously, or the double current in parallel connection. Together with a tiny standby current, this guarantees a long battery life. Protection and diagnostic features support robust and reliable operation. This advanced driver ensures efficient and reliable operation for costeffective and highly competitive solutions.

#### TRINAMIC Motion Control GmbH & Co. KG Hamburg, Germany

#### **APPLICATION EXAMPLES: SIMPLE SOLUTIONS – HIGHLY EFFECTIVE**

The TMC7300 scores with a high power density using integrated power MOSFETs and a complete integrated DC motor control logic, to control velocity and limit torque, or for torque controlled operation. It covers a wide spectrum of applications from battery systems to embedded applications with up to 2A (2.4A) current per motor. Extensive support enables rapid design cycles and fast time-to-market with highly competitive products.

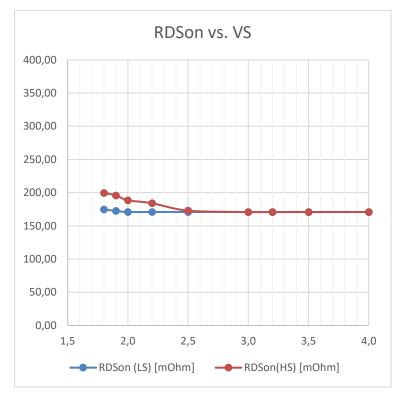

UART INTERFACE FOR CONTROL OF 1 DC MOTOR (UP TO 2.4A)

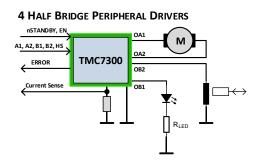

**4 HALF BRIDGE PERIPHERAL DRIVERS**

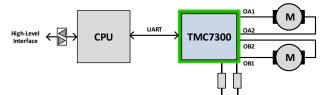

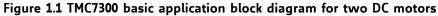

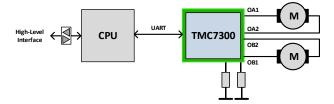

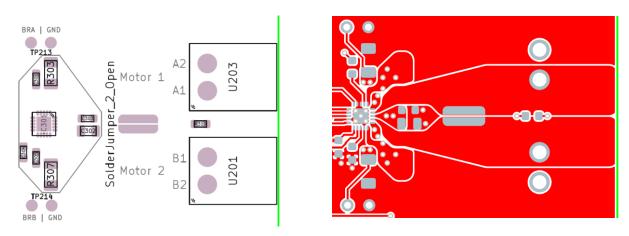

A CPU operates the driver via its UART interface. It configures motor direction and velocity as well as current limit, and accesses diagnostic information via the UART interface. The TMC7300 takes care for voltage and current regulation and overcurrent protection. With single motor operation, output current is increased and power dissipation is reduced.

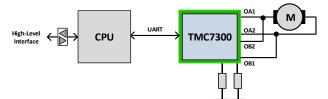

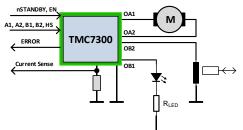

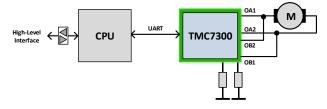

The TMC7300 acts a peripheral driver for a low-voltage application. It drives resistive loads, like a LED, or inductive loads like motors or solenoids. It offers up to 2A peak output current while adding protection features.

**ORDER CODES**

TMC7300-EVAL The is part of TRINAMICs universal evaluation board system which provides a convenient handling of the hardware as well as a user-friendly software tool for evaluation. The TMC7300 evaluation board system consists of three parts: STARTRAMPE (base board), Eselsbrücke (connector board with test points), and TMC7300-EVAL.

| Order code     | PN       | Description                                | Size [mm <sup>2</sup> ] |

|----------------|----------|--------------------------------------------|-------------------------|

| TMC7300-LA     | 00-0191  | Low voltage DC motor driver                | 3 x 3                   |

| TMC7300-LA-T   | 00-0191T | -T denotes tape on reel packing of devices |                         |

| TMC7300-BOB    | 40-0186  | Break out Board with TMC7300               | 20 x 25                 |

| TMC7300-EVAL   | 40-0187  | Evaluation board for TMC7300               | 85 x 55                 |

| ESELSBRÜCKE    | 40-0098  | Connector board fitting to Landungsbrücke  | 61 x 38                 |

| LANDUNGSBRÜCKE | 40-0167  | Baseboard for TMC7300-EVAL and further     | 85 x 55                 |

|                |          | evaluation boards                          |                         |

# **Table of Contents**

| 1 | PRI                             | NCIPLES OF OPERATION4                                                                                                                                     |

|---|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1<br>1.2<br>1.3<br>1.4        | Control Interfaces                                                                                                                                        |

| 2 | PIN                             | ASSIGNMENTS7                                                                                                                                              |

|   | 2.1<br>2.2<br>2.3<br>2.4        | PACKAGE OUTLINE TMC7300 (UART MODE).7<br>SIGNAL DESCRIPTIONS / UART MODE7<br>PACKAGE OUTLINE / HALFBRIDGE MODE8<br>SIGNAL DESCRIPTIONS / HALFBRIDGE MODE8 |

| 3 | SAM                             | IPLE CIRCUITS10                                                                                                                                           |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | DC MOTOR OPERATION                                                                                                                                        |

| 4 | UAR                             | T SINGLE WIRE INTERFACE15                                                                                                                                 |

|   | 4.1<br>4.2<br>4.3<br>4.4        | DATAGRAM STRUCTURE                                                                                                                                        |

| 5 | REG                             | ISTER MAP19                                                                                                                                               |

|   | 5.1<br>5.2<br>5.3               | GENERAL REGISTERS                                                                                                                                         |

| 6 | СНО                             | PPER OPTIONS27                                                                                                                                            |

|   | 6.1<br>6.2                      | LOAD INDICATOR FLAGS27<br>FREEWHEELING AND PASSIVE BRAKING27                                                                                              |

| 7 | SELE                            | CTING SENSE RESISTORS                                                                                                                                     |

|    | 7.1                          | Motor Torque Limit                                                            | 29 |

|----|------------------------------|-------------------------------------------------------------------------------|----|

| 8  | DR                           | IVER DIAGNOSTIC FLAGS                                                         |    |

|    | 8.1<br>8.2<br>8.3            | Temperature Measurement<br>Short Protection<br>Diagnostic Output              |    |

| 9  | QU                           | ICK CONFIGURATION GUIDE                                                       |    |

| 10 | EXT                          | ERNAL RESET                                                                   |    |

| 11 | CLC                          | OCK OSCILLATOR                                                                |    |

| 12 | AB                           | SOLUTE MAXIMUM RATINGS                                                        |    |

| 13 | ELE                          | CTRICAL CHARACTERISTICS                                                       |    |

|    | 13.1<br>13.2<br>13.3         | Operational Range<br>DC and Timing Characteristics<br>Thermal Characteristics | 35 |

| 14 | LAY                          | OUT CONSIDERATIONS                                                            |    |

|    | 14.1<br>14.2<br>14.3<br>14.4 | Exposed Die Pad<br>Wiring GND<br>Supply Filtering<br>Layout Example           |    |

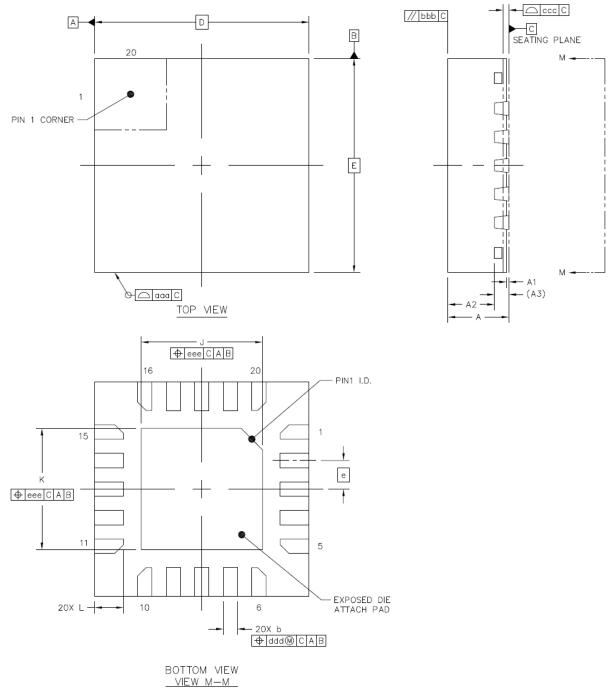

| 15 | PA                           | CKAGE MECHANICAL DATA                                                         | 40 |

|    | 15.1<br>15.2                 | Dimensional Drawings QFN20<br>Package Codes                                   |    |

| 16 | DES                          | SIGNED FOR SUSTAINABILITY                                                     | 42 |

| 17 | TAE                          | BLE OF FIGURES                                                                | 42 |

| 18 | RE\                          | ISION HISTORY                                                                 | 43 |

| 19 | REF                          | ERENCES                                                                       | 43 |

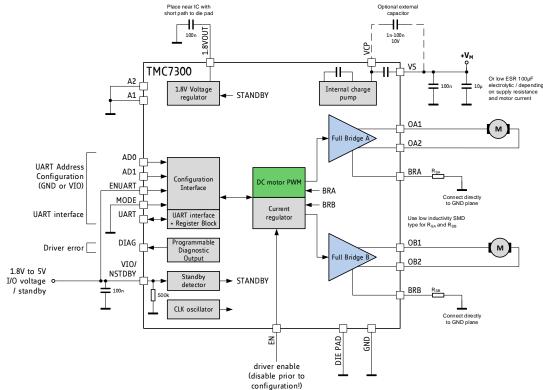

## **1** Principles of Operation

The TMC7300 low voltage motor driver is intended for battery-operated, space- and standby-powercritical driver applications. It is optimized for DC motor control, as well as control of other magnetic actuators or lamp and LED driving. Optionally the driver supplies four protected half-bridges for direct control by four input signals. A highly efficient power stage, boosted by an internal charge pump for best in-class RDSon resistance, provides high motor current from a tiny package even at low supply voltages. With this, dual AA batteries can be drained down to typically 2.0V (voltage must not drop below 1.8V, provide sufficient supply buffer capacitors).

The TMC7300 requires just a few control pins on its tiny package, as full control is possible via UART interface.

Protection and diagnostic features support robust and reliable operation. A simple-to-use 8 bit UART interface opens up more tuning and control options. Industries' most advanced low voltage motor driver family upgrades designs to efficient and reliable operation for cost-effective and highly competitive solutions.

#### MODES OF OPERATION:

#### **OPTION 1: DC-Motor Driver with Full Diagnostics and Control**

This mode allows operation of two DC motors, or a single motor with double current. Options (label <u>UART</u>):

- + Full control over motor velocity and direction by setting PWM voltage for each motor

- + Control motor torque limit for both motors, by setting a common current limit

- + Use current limit to safely avoid battery overload during acceleration or when motor is blocked

- + Detailed diagnostics and thermal management

- + Passive braking and freewheeling for flexible, lowest power stop modes

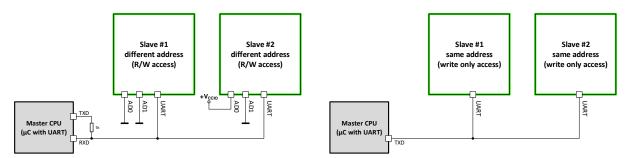

Access to multiple driver ICs is possible using 4 different address settings or via an analog multiplexer IC.

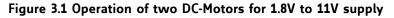

UART INTERFACE FOR CONTROL OF 2 DC MOTORS

UART INTERFACE FOR CONTROL OF 1 DC MOTOR (UP TO 2.4A)

Figure 1.2 UART controlled single or Dual DC motor driver

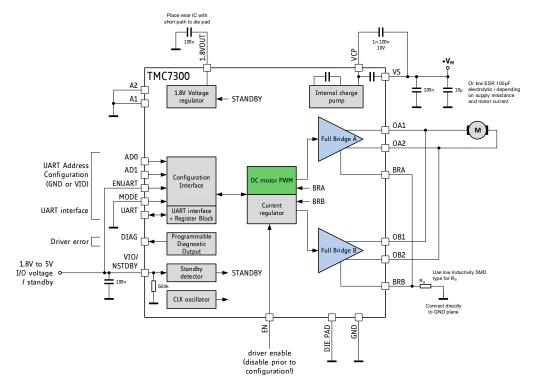

#### **OPTION 2: 4 Half Bridge Peripheral Driver**

This mode uses the power stage to drive inductive or resistive loads. A single-shunt measurement can be realized, using the bridge foot point connections to add a sense resistor. The TMC7300 protects the power stage against overload. An external microcontroller controls each half bridge using a single input / optionally a common high-side PWM.

Figure 1.3 Peripheral Power Driver

### **1.1** Control Interfaces

The TMC7300 supports both, discrete control lines for basic operation and a UART based single wire interface with CRC checking.

#### 1.1.1 UART Interface

The single wire interface allows unidirectional operation (for parameter setting only), or bi-directional operation for full control and diagnostics. It can be driven by any standard microcontroller UART or even by bit banging in software. Baud rates from 9600 Baud to 500k Baud may be used. No baud rate configuration is required, as the TMC7300 automatically adapts to the masters' baud rate. The frame format is identical to the intelligent TRINAMIC controller & driver ICs TMC51XX and TMC22XX. A CRC checksum allows data transmission over longer distance. For fixed initialization sequences, store the data including CRC into the  $\mu$ C, thus consuming only a few 100 bytes of code for a full initialization. CRC may be ignored during read access, if not desired. This makes CRC use an optional feature! The IC has a fixed address selected by 2 pins. Multiple drivers can be programmed in parallel by tying

UART

www.trinamic.com

together all interface pins, in case no read access is required. An optional addressing can be provided by analog multiplexers, like 74HC4066.

From a software point of view the TMC7300 is a peripheral with a number of control and status registers. Most of them can either be written only or are read only. Some of the registers allow both, read and write access. In case read-modify-write access is desired for a write only register, a shadow register can be realized in master software.

### **1.2** Moving and Controlling the Motor

#### 1.2.1 PWM control

The motor is operated by an internal PWM generator. The PWM acts like a dedicated voltage source for the motor. E.g. a 50% duty cycle will let the motor turn like with 50% of the supply voltage. A negated duty cycle will turn the motor in the opposite direction. This way, direction and velocity can be controlled like with a programmable power source. By slowly increasing / decreasing the duty cycle, the motor can be softly accelerated and decelerated.

#### 1.2.2 Internal Current Limiter

When a DC-motor is mechanical loaded, its current increases. Therefore, a current limit allows limitation of motor torque. At the same time, the power source, e.g. a dual AA battery with a certain internal resistance is protected against voltage drop due to overload. This feature especially is helpful when moving the motor to a mechanical obstacle. The action of the current limiter can be read back via the interface.

### 1.3 Mechanical Load Sensing

When a DC-motor is mechanical loaded, its current increases. Therefore, a current limit allows limitation of motor torque. The TMC7300 reports back, when this load limit is achieved. This feature especially is helpful when moving the motor to a mechanical obstacle.

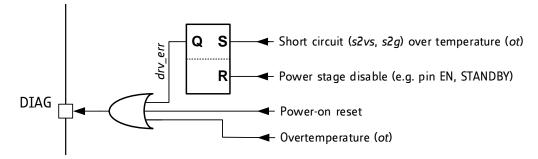

### **1.4** Protection and Diagnostics

By adapting the sense resistor to the desired maximum current, a sensitive protection of the respective half bridge is reached. In case the voltage drop across the sense resistor plus internal Power MOSFET exceeds roughly 1V, the power stage becomes disabled and the error is reported via the interface, or via the DIAG output.

## 2 Pin Assignments

The TMC7300 comes in a tiny package in order to fit miniaturized devices. For the ease of use, pinning is shown separately for all four function-modes.

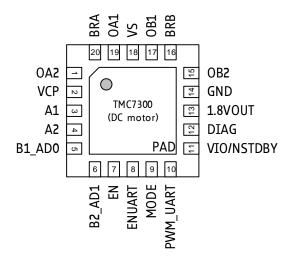

### 2.1 Package Outline TMC7300 (UART mode)

Figure 2.1 TMC7300 Pinning Top View Stepper Driver - QFN20, 3x3mm<sup>2</sup>, 0.4mm pitch

### 2.2 Signal Descriptions / UART mode

| Pin        | Number | Туре | Function                                                                                                                                                      |

|------------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0A2        | 1      |      | DC motor 1 output 2                                                                                                                                           |

| VCP        | 2      |      | Charge pump voltage. Optionally tie to VS using 1nF to 100nF capacitor. May be left unconnected in stepper mode.                                              |

| A1         | 3      | DI   | A1 input not used in UART mode (tie to GND or VCC_IO)                                                                                                         |

| A2         | 4      | DI   | A2 input not used in UART mode (tie to GND or VCC_IO)                                                                                                         |

| B1_AD0     | 5      | DI   | Selection of UART Address 03 (AD0=LSB, AD1=MSB)                                                                                                               |

| B2_AD1     | 6      | DI   |                                                                                                                                                               |

| EN         | 7      | DI   | Enable input. The power stage becomes switched off (all motor outputs floating) when this pin becomes driven to a low level. Also used to clear error flags.  |

| ENUART     | 8      | DI   | Mode selection input.<br>ENUART, MODE:<br>01: 4 Halfbridge<br>10: UART enabled                                                                                |

| MODE       | 9      | DI   | (CLK, TST input in factory test mode)                                                                                                                         |

| PWM_UART   | 10     | DIO  | UART Input/Output.                                                                                                                                            |

| VIO/NSTDBY | 11     |      | 1.8V to 5V IO supply voltage for all digital pins. IC goes to standby mode and resets, when this pin is pulled to GND.                                        |

| DIAG       | 12     | DO   | Diagnostic output. High level upon driver error or stall. Reset by EN=low.                                                                                    |

| 1.8VOUT    | 13     |      | Output of internal 1.8V regulator. Attach 100nF ceramic capacitor to GND near to pin for best performance. Provide the shortest possible loop to the GND pad. |

| GND        | 14     |      | GND. Connect to GND plane near pin.                                                                                                                           |

| OB2        | 15     |      | DC motor 2 output 2                                                                                                                                           |

| BRB        | 16     |      | Sense resistor connection for coil B or DC motor 2. Place sense resistor to GND near pin.                                                                     |

| OB1        | 17     |      | DC motor 2 output 1                                                                                                                                           |

| Pin                | Number | Туре | Function                                                                                                     |

|--------------------|--------|------|--------------------------------------------------------------------------------------------------------------|

| VS                 | 18     |      | Motor supply voltage. Provide filtering capacity >10µF near pin with shortest possible loop to GND pad.      |

| 0A1                | 19     |      | DC motor 1 output 2                                                                                          |

| BRA                | 20     |      | Sense resistor connection for coil A or DC motor 1. Place sense resistor to GND near pin.                    |

| Exposed<br>die pad | -      |      | Connect the exposed die pad to a GND plane. Provide as many as possible vias for heat transfer to GND plane. |

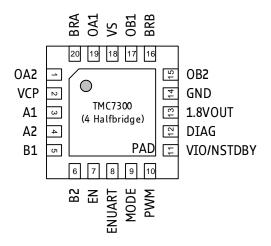

## 2.3 Package Outline / Halfbridge mode

Figure 2.2 TMC7300 Pinning Top View Stepper Driver - QFN20, 3x3mm<sup>2</sup>, 0.4mm pitch

| 2.4 | Sig | nal D | escripti | ons / | Halfbridge | mode |

|-----|-----|-------|----------|-------|------------|------|

|     |     |       |          |       |            |      |

| Pin        | Number | Туре | Function                                                                                                                                                                       |  |  |  |  |  |  |  |

|------------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 0A2        | 1      |      | Bridge A output 2                                                                                                                                                              |  |  |  |  |  |  |  |

| VCP        | 2      |      | Charge pump voltage. Optionally tie to VS using 1nF to 100nF capacitor. May be left unconnected if maximum 2 pins change at a time.                                            |  |  |  |  |  |  |  |

| A1         | 3      | DI   | Bridge A output 1 polarity                                                                                                                                                     |  |  |  |  |  |  |  |

| A2         | 4      | DI   | Bridge A output 2 polarity                                                                                                                                                     |  |  |  |  |  |  |  |

| B1         | 5      | DI   | Bridge B output 1 polarity                                                                                                                                                     |  |  |  |  |  |  |  |

| B2         | 6      | DI   | Bridge B output 2 polarity                                                                                                                                                     |  |  |  |  |  |  |  |

| EN         | 7      | DI   | Enable input. The power stage becomes switched off (all motor outputs floating) when this pin becomes driven to a low level. Also used to release driver after fault shutdown. |  |  |  |  |  |  |  |

| ENUART     | 8      | DI   | tie to GND                                                                                                                                                                     |  |  |  |  |  |  |  |

| MODE       | 9      | DI   | tie to VIO                                                                                                                                                                     |  |  |  |  |  |  |  |

| PWM        | 10     | DI   | Common PWM for high-side drivers. Tie high to enable high-side drivers as controlled by A and B inputs. Influences high-side driver, only.                                     |  |  |  |  |  |  |  |

| VIO/NSTDBY | 11     |      | 1.8V to 5V IO supply voltage for all digital pins. IC goes to standby mode and resets, when this pin is pulled to GND.                                                         |  |  |  |  |  |  |  |

| DIAG       | 12     | DO   | Diagnostic output. High level upon driver error. Reset by EN=low.                                                                                                              |  |  |  |  |  |  |  |

| 1.8VOUT    | 13     |      | Output of internal 1.8V regulator. Attach 100nF ceramic capacitor to GND near to pin for best performance. Provide the shortest possible loop to the GND pad.                  |  |  |  |  |  |  |  |

| Pin                | Number | Туре | Function                                                                                                              |

|--------------------|--------|------|-----------------------------------------------------------------------------------------------------------------------|

| GND                | 14     |      | GND. Connect to GND plane near pin.                                                                                   |

| OB2                | 15     |      | Bridge B output 2                                                                                                     |

| BRB                | 16     |      | Foot point of bridge B. Connect to GND directly, or via a sense resistor, if external current measurement is desired. |

| OB1                | 17     |      | Bridge B output 1                                                                                                     |

| VS                 | 18     |      | Bridge supply voltage. Provide filtering capacity >10µF near pin with shortest possible loop to GND pad.              |

| 0A1                | 19     |      | Bridge A output 1                                                                                                     |

| BRA                | 20     |      | Foot point of bridge A. Connect to GND directly, or via a sense resistor.                                             |

| Exposed<br>die pad | -      |      | Connect the exposed die pad to a GND plane. Provide as many as possible vias for heat transfer to GND plane.          |

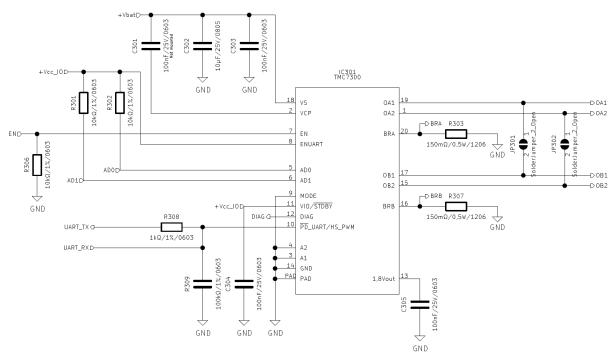

# 3 Sample Circuits

The sample circuits show the connection of external components in different operation and supply modes. The connection of the bus interface and further digital signals is left out for clarity. The TMC7300 is configured for different application modes by two pins, as well as by settings available via the UART interface.

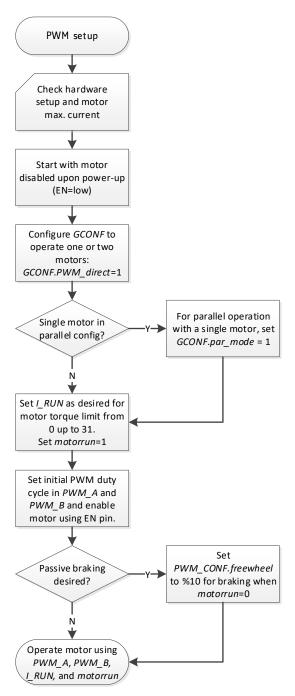

## 3.1 DC Motor Operation

The standard application circuit uses a minimum set of additional components to operate one or two DC motors. Each one sense resistor sets the motor current limit. See chapter 7 to choose the right sense resistor value. Take care to keep power supply ripple due to chopper operation at a few 100mV, max., especially when low voltage operation is desired. Use ceramic, or low ESR capacitors for filtering the power supply. The capacitors need to cope with the current ripple caused by chopper operation. A minimum capacity of  $100\mu$ F electrolytic, or a  $10\mu$ F ceramic capacitor near the driver is recommended to keep ripple low. Actual demand will depend on the internal power supply resistance and the desired motor current. VCC\_IO can be supplied from a separate supply, e.g. a 3.3V regulator, or be driven by a microcontroller port pin. ADO and AD1 set the UART address. Ensure, that the EN pin is driven by the microcontroller in order to disable the motor prior to initialization! Apply a pulldown resistor for EN to keep it low during power-up.

#### Basic layout and component hints

Place sense resistors and all filter capacitors as close as possible to the related IC pins. Use a solid common GND for all GND connections, also for sense resistor GND. Connect 1.8VOUT filtering capacitor directly to 1.8VOUT and the GND pin. See layout hints for more details. Low ESR electrolytic capacitors are recommended for VS filtering unless supply resistance is very low.

#### Attention

Power up with EN-pin low. Set *GCONF.pwm\_direct* prior to enabling the driver via EN-pin. Otherwise the motor will run directly after power-up.

#### Figure 3.2 Operation of a single DC-Motor (double current)

A single DC-motor can be operated at double current (up to 2.4A), by paralleling both power-stages. Before operating the motor, the IC has to be switched to parallel mode, because default setting will cause a short circuit between the bridges and a high current flow, which will trigger overcurrent protection. Therefore ensure, that the EN pin is driven by the microcontroller in order to disable the motor prior to initialization. Apply a pulldown resistor for EN additionally to ensure power-up with a low level.

#### Attention

For parallel operation, power up with EN-pin low. Set *GCONF.par\_mode* in order to force identical drive signals <u>prior</u> to enabling the driver via EN-pin. In this mode, a capacitor is required on pin VCP.

### 3.2 Halfbridge Driver Mode

Halfbridge driver mode offers four separate half-bridges to individually drive and control resistive and inductive loads, like LEDs, solenoids, etc. In case a current measurement is desired, each two halfbridges allow adding a foot point shunt resistor. Keep voltage drop in this resistor to maximum 400mV for normal operation. A common high-side PWM input allows switching off all high-side drivers at the same time. It does not influence drivers, where the low-side is on. If more than two drivers are switched at the same time, a capacitor on pin VCP is recommended. The diagnostic output signals any overcurrent or overtemperature condition. The driver automatically restarts after power-up, or after cycling VIO\_NSTDBY pin.

Figure 3.3 Halfbridge Driver Mode

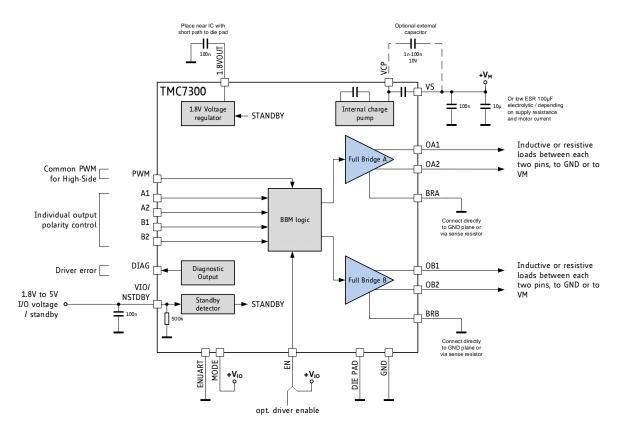

## 3.3 Highly Efficient Driver

The TMC7300 integrates a highly efficient power stage, offering low RDSon even at low supply voltages, due to its internal charge pump. This enables high motor current drive capability and low power dissipation for battery powered applications.

Figure 3.4 RDSon Variation over Supply Voltage

When operating at a high motor current, the driver power dissipation due to MOSFET switch onresistance significantly heats up the driver. This power dissipation will significantly heat up the PCB cooling infrastructure, if operated at an increased duty cycle. This in turn leads to a further increase of driver temperature. An increase of temperature by about 100°C increases MOSFET resistance by roughly 50%. This is a typical behavior of MOSFET switches. Therefore, under high duty cycle, high load conditions, thermal characteristics have to be carefully taken into account, especially when increased environment temperatures are to be supported. Refer the thermal characteristics and the layout hints for more information. As a thumb rule, thermal properties of the PCB design become critical for the tiny QFN 3mm x 3mm package at or above 0.8A mean motor current for increased periods of time. For currents above 0.8A, a 4-layer PCB layout with 5 via contact of the die attach pad to the GND plane is required. Keep in mind that resistive power dissipation raises with the square of the motor current. On the other hand, this means that a small reduction of motor current significantly saves heat dissipation and energy.

Pay special attention to good thermal properties of your PCB layout, when going for 0.8A mean current or more.

### 3.4 Low Power Standby

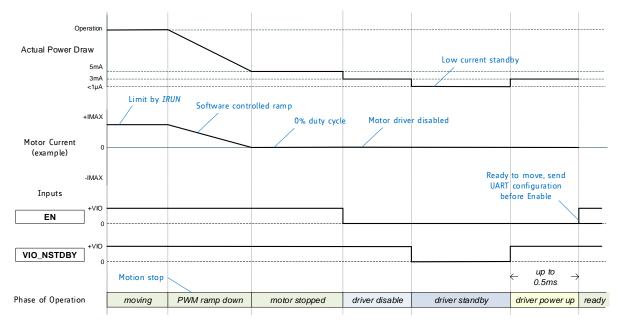

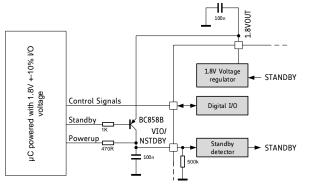

Battery powered applications, as well as mains powered applications conforming to EU energy saving regulations, often require a standby mode, where the power-supply remains on. Current consumption in this mode must be minimized. Control near zero power TMC7300 standby operation by switching off the I/O supply voltage on VIO\_NSTDBY pin. At the same time make sure, that no digital input pin is at a high level. An input level above VIO\_NSTDBY would hinder pulling down VIO\_NSTDBY, due to the ESD protection diodes in each digital I/O pin. These diodes clamp each input to a level between GND and the IO supply voltage VIO\_NSTDBY. Therefore, stop the motor first, and allow sufficient time for the motor to come to a standstill, pull the enable input EN low, and also all other input pins, to switch off the motor completely before switching off VIO voltage. All driver registers are reset to their power-up defaults after leaving standby mode. See Figure 3.5.

Figure 3.5 Switching to Standby and Back On

### 3.5 Very low I/O voltage operation

In cases, where an I/O voltage of 1.8V (or even lower, due to tolerance) is to be used, the VIO undervoltage threshold level might be too high, to safely release the TMC7300 from reset state. A simple way to avoid the need for an additional I/O voltage regulator (e.g. 2V type), is to use the internal 1.8V regulator to self-supply the TMC7300 VIO pin. In order to allow power-up, the voltage on pin at VIO/NSTDBY has to be forced to min. 1.4V. In order to go back to low power standby, pull it down to less than 0.6V. A PNP transistor gives a low resistive switch to supply VIO.

Figure 3.6 Additional Circuit for I/O voltage <1.80V

# 4 UART Single Wire Interface

15

The UART single wire interface allows control of the TMC7300 with any microcontroller UART. It shares transmit and receive line like an RS485 based interface. Data transmission is secured using a cyclic redundancy check, so that increased interface distances (e.g. over cables between two PCBs) can be bridged without danger of wrong or missed commands even in the event of electro-magnetic disturbance. The automatic baud rate detection makes this interface easy to use.

## 4.1 Datagram Structure

#### 4.1.1 Write Access

|   |                                                     |   |    |                                            |   | UA | ART V | <b>V</b> RITE                   | ACCESS | 5 DATA                 | GRAM | STRUC        | TURE                         |      |                                |    |      |     |    |

|---|-----------------------------------------------------|---|----|--------------------------------------------|---|----|-------|---------------------------------|--------|------------------------|------|--------------|------------------------------|------|--------------------------------|----|------|-----|----|

|   | each byte is LSBMSB, highest byte transmitted first |   |    |                                            |   |    |       |                                 |        |                        |      |              |                              |      |                                |    |      |     |    |

|   | 0 63                                                |   |    |                                            |   |    |       |                                 |        |                        |      |              |                              |      |                                |    |      |     |    |

|   | sync + reserved                                     |   |    |                                            |   |    |       |                                 |        | 8 bit slave<br>address |      |              | RW + 7 bit<br>register addr. |      |                                | ta | CRC  |     |    |

|   |                                                     |   | 0. | .7                                         |   |    |       | 815                             |        |                        | 1623 |              |                              | 2455 |                                |    | 5663 |     |    |

| 1 | 0                                                   | 1 | 0  | Reserved (don't cares but included in CRC) |   |    |       | <i>SLAVEADDR</i> =(MS2,<br>MS1) |        |                        |      | ster<br>ress | 1                            |      | bytes 3,<br>high to l<br>byte) |    |      | CRC |    |

| 0 | 1                                                   | 2 | 3  | 4                                          | 5 | 9  | ٢     | 8                               | I      | 15                     | 16   | :            | 23                           | 24   |                                | 55 | 56   | I   | 63 |

A sync nibble precedes each transmission to and from the TMC7300 and is embedded into the first transmitted byte, followed by an addressing byte (0 to 3, selected by pins MS1 (LSB) and MS2 for TMC7300). Each transmission allows a synchronization of the internal baud rate divider to the master clock. The actual baud rate is adapted and variations of the internal clock frequency are compensated. Thus, the baud rate can be freely chosen within the valid range. Each transmitted byte starts with a start bit (logic 0, low level on UART pin) and ends with a stop bit (logic 1, high level on UART pin). The bit time is calculated by measuring the time from the beginning of start bit (1 to 0 transition) to the end of the sync frame (1 to 0 transition from bit 2 to bit 3). All data is transmitted bytewise. The 32 bit data words are transmitted with the highest byte first.

A minimum baud rate of 9000 baud is permissible, assuming maximum clock frequency (worst case for low baud rate). Maximum baud rate is  $f_{CLK}/16$  due to the required stability of the baud clock.

The slave address *SLAVEADDR* is selected by MS1 (bit 0) and MS2 (bit 1) in the range 0 to 3. Bit 7 of the register address identifies a Read (0) or a Write (1) access. Example: Address 0x10 is changed to 0x90 for a write access.

The communication becomes reset if a pause time of longer than 63 bit times between the start bits of two successive bytes occurs. This timing is based on the last correctly received datagram. In this case, the transmission needs to be restarted after a failure recovery time of minimum 12 bit times of bus idle time. This scheme allows the master to reset communication in case of transmission errors. Any pulse on an idle data line below 16 clock cycles will be treated as a glitch and leads to a timeout of 12 bit times, for which the data line must be idle. Other errors like wrong CRC are also treated the same way. This allows a safe re-synchronization of the transmission after any error conditions. Remark, that due to this mechanism an abrupt reduction of the baud rate to less than 15 percent of the previous value is not possible.

Each accepted write datagram becomes acknowledged by the receiver by incrementing an internal cyclic datagram counter (8 bit). Reading out the datagram counter allows the master to check the success of an initialization sequence or single write accesses. Read accesses do not modify the counter.

The UART line must be logic high during idle state.

#### 4.1.2 Read Access

|   |                                                     |    |        |        | l                | JART | Read | ACCES | S REQUEST D   | ATAGR | RAM ST | TRUCTURE                       |    |      |     |    |

|---|-----------------------------------------------------|----|--------|--------|------------------|------|------|-------|---------------|-------|--------|--------------------------------|----|------|-----|----|

|   | each byte is LSBMSB, highest byte transmitted first |    |        |        |                  |      |      |       |               |       |        |                                |    |      |     |    |

|   |                                                     | sy | nc + r | eserve | ed               |      |      | 8 bi  | t slave addı  | ess   |        | RW + 7 bit register<br>address | r  | CRC  |     |    |

|   |                                                     |    | 0.     | 7      |                  |      |      |       | 815           |       |        | 1623                           |    | 2431 |     |    |

| 1 | 0                                                   | 1  | 0      |        | rved (<br>includ |      |      | SLAV  | /EADDR=(MS2,I | 4S1)  |        | register address               | 0  |      | CRC |    |

| 0 | 1                                                   | 2  | Э      | 4      | 5                | 9    | 7    | 8     | :             | 15    | 16     | i                              | 23 | 24   | ÷   | 31 |

The read access request datagram structure is identical to the write access datagram structure, but uses a lower number of user bits. Its function is the addressing of the slave and the transmission of the desired register address for the read access. The TMC2300 responds with the same baud rate as the master uses for the read request.

In order to ensure a clean bus transition from the master to the slave, the TMC2300 does not immediately send the reply to a read access, but it uses a programmable delay time after which the first reply byte becomes sent following a read request. This delay time can be set in multiples of eight bit times using *SENDDELAY* time setting (default=8 bit times) according to the needs of the master.

|                 |                                                     |   |    |   |        | UAR    | T Rea                   | d acc | ess re | PLY D | ATAGE                        | RAM ST       | ructi | JRE        |                          |      |     |     |    |

|-----------------|-----------------------------------------------------|---|----|---|--------|--------|-------------------------|-------|--------|-------|------------------------------|--------------|-------|------------|--------------------------|------|-----|-----|----|

|                 | each byte is LSBMSB, highest byte transmitted first |   |    |   |        |        |                         |       |        |       |                              |              |       |            |                          |      |     |     |    |

|                 | 0 63                                                |   |    |   |        |        |                         |       |        |       |                              |              |       |            |                          |      |     |     |    |

| sync + reserved |                                                     |   |    |   |        |        | 8 bit master<br>address |       |        |       | RW + 7 bit<br>register addr. |              |       | 32 bit dat | a                        |      | CRC |     |    |

|                 |                                                     |   | 0. | 7 |        |        |                         | 815   |        |       | 1623                         |              | 2455  |            |                          | 5663 |     |     |    |

| 1               | 0                                                   | 1 | 0  |   | reserv | ed (0) |                         |       | 0xFF   |       |                              | ster<br>ress | 0     |            | bytes 3, 2<br>h to low b |      |     | CRC |    |

| 0               | 1                                                   | 2 | 3  | 4 | 5      | 6      | 7                       | 8     | :      | 15    | 16                           | :            | 23    | 24         | :                        | 55   | 56  | :   | 63 |

The read response is sent to the master using address code %11111111. The transmitter becomes switched inactive four bit times after the last bit is sent.

Address %11111111 is reserved for read access replies going to the master.

Hint

Find an example for generating read and write datagrams in the TMC2300 calculation sheet.

### 4.2 CRC Calculation

An 8 bit CRC polynomial is used for checking both read and write access. It allows detection of up to eight single bit errors. The CRC8-ATM polynomial with an initial value of zero is applied LSB to MSB, including the sync- and addressing byte. The sync nibble is assumed to always be correct. The TMC7300 responds only to correctly transmitted datagrams containing its own slave address. It increases its datagram counter for each correctly received write access datagram.

$$CRC = x^8 + x^2 + x^1 + x^0$$

#### SERIAL CALCULATION EXAMPLE

CRC = (CRC << 1) OR (CRC.7 XOR CRC.1 XOR CRC.0 XOR [new incoming bit])

```

C-CODE EXAMPLE FOR CRC CALCULATION

void swuart_calcCRC(UCHAR* datagram, UCHAR datagramLength)

int i,j;

UCHAR* crc = datagram + (datagramLength-1); // CRC located in last byte of message

UCHAR currentByte:

*crc = 0;

for (i=0; i<(datagramLength-1); i++) {</pre>

// Execute for all bytes of a message

currentByte = datagram[i];

// Retrieve a byte to be sent from Array

for (j=0; j<8; j++) {

if ((*crc >> 7) ^ (currentByte&0x01))

// update CRC based result of XOR operation

{

* crc = (* crc << 1) ^ 0 x 07;

}

else

{

*crc = (*crc << 1);

}

currentByte = currentByte >> 1;

// for CRC bit

}

// for message byte

```

### 4.3 UART Signals

The UART interface on the TMC7300 uses a single bi-direction pin:

| UART INTERFACE SIGNAL |                                                                                |  |  |

|-----------------------|--------------------------------------------------------------------------------|--|--|

| UART                  | Non-inverted data input and output. I/O with Schmitt Trigger and VCC_IO level. |  |  |

| AD0                   | IC UART address bit 0 (LSB)                                                    |  |  |

| AD1                   | IC UART address bit 1                                                          |  |  |

The IC checks PDN\_UART for correctly received datagrams with its own address continuously. It adapts to the baud rate based on the sync nibble, as described before. In case of a read access, it switches on its output drivers and sends its response using the same baud rate. The output becomes switched off four bit times after transfer of the last stop bit.

Figure 4.1 Attaching the TMC7300 to a microcontroller UART

### 4.4 Addressing Multiple Slaves

#### WRITE ONLY ACCESS

If read access is not used, and all slaves are to be programmed with the same initialization values, no addressing is required. All slaves can be programmed in parallel like a single device (Figure 4.1.).

#### ADDRESSING MULTIPLE SLAVES

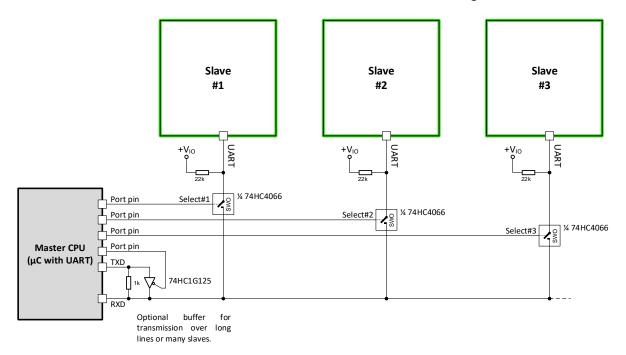

As the TMC7300 uses has a limited number of UART addresses, in principle only up to four ICs can be accessed per UART interface channel. Adding analog switches allows separated access to individual ICs. This scheme is similar to an SPI bus with individual slave select lines (Figure 4.2).

#### Figure 4.2 Addressing multiple TMC7300 via single wire interface using analog switches

PROCEED AS FOLLOWS TO CONTROL MULTIPLE SLAVES:

- Set the UART to 8 bits, no parity. Select a baud rate safely within the valid range. At 250kBaud, a write access transmission requires 320µs (=8 Bytes \* (8+2) bits \* 4µs).

- Before starting an access, activate the select pin going to the analog switch by setting it high. All other slaves select lines shall be off, unless a broadcast is desired.

- When using the optional buffer, set TMC7300 transmission send delay to an appropriate value allowing the µC to switch off the buffer before receiving reply data.

- To start a transmission, activate the TXD line buffer by setting the control pin low.

- When sending a read access request, switch off the buffer after transmission of the last stop bit is finished.

- Take into account, that all transmitted data also is received by the RXD input.

# 5 Register Map

This chapter gives an overview of the complete register set. Some of the registers bundling a number of single bits are detailed in extra tables. The functional practical application of the settings is detailed in dedicated chapters.

#### Note

- *Reset default*: All registers become reset to 0 upon power up, unless otherwise noted. - Add 0x80 to the address **Addr** for write accesses!

| NOTATION OF HEXADECIMAL AND BINARY NUMBERS  |                                               |  |  |  |

|---------------------------------------------|-----------------------------------------------|--|--|--|

| 0x precedes a hexadecimal number, e.g. 0x04 |                                               |  |  |  |

| %                                           | precedes a multi-bit binary number, e.g. %100 |  |  |  |

| NOTATION OF R/W FIELD |                             |  |  |

|-----------------------|-----------------------------|--|--|

| R                     | Read only                   |  |  |

| W                     | Write only                  |  |  |

| R/W                   | Read- and writable register |  |  |

| R+C                   | Clear upon read             |  |  |

#### **OVERVIEW REGISTER MAPPING**

| REGISTER                        | DESCRIPTION                                                                                                                                                                     |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Configuration Registers | These registers contain<br>- global configuration<br>- global status flags<br>- interface configuration                                                                         |

| Chopper Register Set            | This register set offers registers for<br>- chopper settings, e.g. frequency<br>- passive braking and freewheeling options<br>- driver diagnostics<br>- driver enable / disable |

| Motor Control Registers         | Register set for actual control of motor operation                                                                                                                              |

# 5.1 General Registers

| GENER    | GENERAL CONFIGURATION REGISTERS (0x000x0F)  |    |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|----------|---------------------------------------------|----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| R/W      | R/W Addr n Register Description I bit names |    |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|          |                                             |    | <b>_</b>  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| RW       | 0×00                                        | 10 | GCONF     | Bit       GCONF - Global configuration flags         0       PWM_direct (Reset default=0)         0:       Do not use this mode.         1:       Normal DC-motor operation         Attention: Do not enable driver prior to setting this flag. Motors 1 would start running.         1       extcap (Reset default=0)         0:       Operation without external capacitor on VCP.         1:       External capacitor available. No switching delays.         2       par_mode (Reset default=0)         0:       normal operation (dual motor)         1:       Single DC-motor operation: Parallel operation for single motor. Bridge OA1 and OB1, OA2 and OB2 output identical signals. Control is by bridge A, only. Externally bridge the outputs and the sense resistor connection.         Attention: Do not enable driver prior to setting this flag, if outputs are bridged!         3       reserved / set to 0         4       reserved / set to 0         5       reserved / set to 0         6       reserved / set to 0 |  |  |

|          |                                             |    |           | 7       test_mode         0:       Normal operation         1:       Enable analog test output on pin DIR         IHOLD[10] selects the function of DIR:         01:       T120, DAC         Attention:       Not for user, set to 0 for normal operation!         Bit       GSTAT - Global status flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|          |                                             |    |           | (Re-Write with '1' bit to clear respective flags)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|          |                                             |    | GSTAT     | 0 <i>reset</i><br>1: Indicates that the IC has been reset since the last<br>read access to <i>GSTAT</i> . All registers have been<br>cleared to reset values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| R+<br>WC | 0x01                                        | 3  |           | 1 drv_err<br>1: Indicates, that the driver has been shut down<br>due to overtemperature or short circuit detection<br>since the last read access. Read DRV_STATUS for<br>details. The flag can only be cleared when all<br>error conditions are cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|          |                                             |    |           | <ul> <li>2 u3v5</li> <li>1: Actual state of the supply voltage comparator. A high value means that the voltage sinks below 3.5V. This flag is not latched and thus does not need to be cleared.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| R        | 0x02                                        | 8  | IFCNT     | Interface transmission counter. This register becomes<br>incremented with each successful UART interface write<br>access. Read out to check the serial transmission for<br>lost data. Read accesses do not change the content.<br>The counter wraps around from 255 to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| W        | 0x03                                        | 4  | SLAVECONF | Bit SLAVECONF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| GENERAL CONFIGURATION REGISTERS (0x000x0F) |      |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                          |  |  |

|--------------------------------------------|------|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| R/W                                        | Addr | n            | Register | Descri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Description I bit names                                                                                                                                                                                                                                                                  |  |  |

|                                            |      |              |          | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>SENDDELAY for read access (time until reply is sent):</li> <li>0, 1: 8 bit times</li> <li>2, 3: 3*8 bit times</li> <li>4, 5: 5*8 bit times</li> <li>6, 7: 7*8 bit times</li> <li>8, 9: 9*8 bit times</li> <li>10, 11: 11*8 bit times</li> <li>12, 13: 13*8 bit times</li> </ul> |  |  |

|                                            |      |              |          | Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14, 15: 15*8 bit times <b>INPLIT</b> (Reads the state of all input pins available)                                                                                                                                                                                                       |  |  |

| R                                          | 0x06 | 10<br>+<br>8 | IOIN     | Bit       INPUT (Reads the state of all input pins available)         0       EN (1=enable driver)         1       NSTDBY (0=standby, 1=enable)         2       AD0         3       AD1         4       DIAG         5       1: UART interface on         6       UART input         7       MODE input         0: UART controlled operation         8       A2         9       A1         10       COMP_A1A2         1: during LS passive braking: A1 voltage > A2 volta         11       COMP B1B2 |                                                                                                                                                                                                                                                                                          |  |  |

|                                            |      |              |          | 31<br>24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1: during LS passive braking: B1 voltage > B2 voltage<br>VERSION: 0x40=first version of the IC<br>Identical numbers mean full digital compatibility.                                                                                                                                     |  |  |

## 5.2 Motor Control

| MOTOR CONTROL REGISTER SET (0x100x1F) |   |                                                               |                                                               |                                                                                                                                                                                                         |  |

|---------------------------------------|---|---------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Addr                                  | n | Register                                                      | Description / bit names                                       |                                                                                                                                                                                                         |  |

|                                       |   |                                                               | Bit                                                           | CURRENT_LIMIT - Driver current control                                                                                                                                                                  |  |

|                                       |   |                                                               | 0                                                             | motorrun (Reset default=1)                                                                                                                                                                              |  |

|                                       |   |                                                               |                                                               | 1: Normal motor operation                                                                                                                                                                               |  |

|                                       |   |                                                               |                                                               | 0: Enable freewheeling options. The motor becomes                                                                                                                                                       |  |

|                                       |   |                                                               |                                                               | stopped in case freewheeling or passive braking is                                                                                                                                                      |  |

|                                       |   |                                                               |                                                               | selected (PWM_CONF).                                                                                                                                                                                    |  |

|                                       | 1 |                                                               | 128                                                           | IRUN (Reset default=31)                                                                                                                                                                                 |  |

| W 0x10                                |   | _                                                             |                                                               | Run current limit for both motors                                                                                                                                                                       |  |

| •//=•                                 | 5 | LIMIT                                                         |                                                               | (0=1/32 31=32/32)                                                                                                                                                                                       |  |

|                                       | _ |                                                               |                                                               | Set a lower value to limit motor torque. Each full                                                                                                                                                      |  |

|                                       |   |                                                               |                                                               | bridge current is individually cycle by cycle limited                                                                                                                                                   |  |

|                                       |   |                                                               |                                                               | by <i>IRUN</i> setting. When current limiting is <i>not</i> active,                                                                                                                                     |  |

|                                       |   |                                                               |                                                               | OLA resp. OLB become set.                                                                                                                                                                               |  |

|                                       |   |                                                               |                                                               | Wint Channe and maintain in a way that named                                                                                                                                                            |  |

|                                       |   |                                                               |                                                               | <i>Hint:</i> Choose sense resistors in a way, that normal <i>IRUN</i> is 16 to 31 for best performance.                                                                                                 |  |

|                                       |   |                                                               | Ri+                                                           | PWM_DIRECT - Driver current control                                                                                                                                                                     |  |

|                                       | 9 |                                                               |                                                               | PWM A, signed: Bridge A PWM duty cycle                                                                                                                                                                  |  |

| 0~22                                  |   | PIN/M AR                                                      | 00                                                            | (-255 to +255 => -100% to +100%)                                                                                                                                                                        |  |

| UNEL                                  |   |                                                               | 24 16                                                         | PWM B, signed: Bridge B PWM duty cycle                                                                                                                                                                  |  |

|                                       | , |                                                               | 2410                                                          | (-255 to +255 => -100% to +100%)                                                                                                                                                                        |  |

|                                       |   | Addr         n           0x10         1           +         5 | AddrnRegister0x101<br>+<br>5CURRENT_<br>LIMIT0x229<br>+PWM_AB | Addr       n       Register       Description         Bit       0         0x10       1       6         1       CURRENT_LIMIT       128         0x10       9       Bit         0x22       +       PWM_AB |  |

# 5.3 Chopper Control Registers

| Снорр  | CHOPPER CONTROL REGISTER SET (0x6C0x7F)                   |          |                                                 |                                  |                |

|--------|-----------------------------------------------------------|----------|-------------------------------------------------|----------------------------------|----------------|

| R/W    | R/W Addr n <i>Register</i> Description <i>I bit names</i> |          |                                                 | Range [Unit]                     |                |

| RW     | 0x6C                                                      | 32       | CHOPCONF                                        | Chopper and driver configuration | Reset default= |

| IX V V | UXOC                                                      | 52       | CHOPCONF                                        | See separate table!              | 0x13008001     |